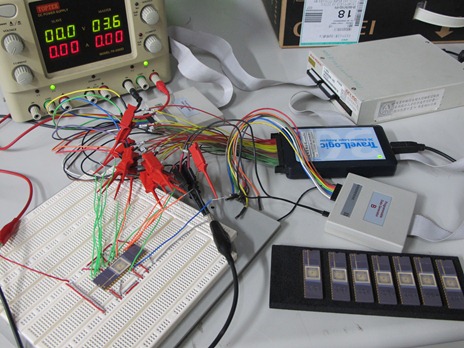

這兩天超忙,別人是要補上班上課一天,我則是兩天都在加班,雖然早上不用很早出門,但晚上幾乎都很晚回家,平均都十二天才離開。 禮拜六是回到學校量測晶片,而禮拜天則到公司修錯誤補進度。前面的測試是之前計畫約好的,但後面的加班實在是飛來橫禍。 之前還在唸書的時候,就很羨慕別人有晶片下線的機會,畢竟身上也學了一些功夫,但卻無用武之地,令人有種懷才不遇的遺憾。幸好,在畢業離開學校之前,有了這次機會達到下線的目的。儘管這是大學部的課程,沒辦法算入畢業學分,但我仍舊甘之如飴,只因為所求只為下線而已。 晶片設計的過程還算順利,畢竟這幾年裡,有好幾個晚上通宵達旦的努力,打下了堅厚的基礎,唯一比較麻煩的,主要在了解演算法而已。當時一邊要趕自己的論文,一邊要找時間研讀其他領域的知識並實現該晶片,蠟燭兩頭燒,還好關關難過關關過。 這次下線回來,終於有了自己從頭到尾設計的第一顆實體晶片,尤其在最後量測完,發現沒有明顯的錯誤存在,不只令人感到,更讓人自豪。